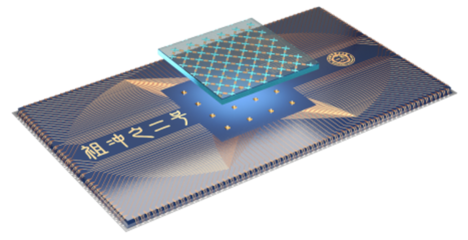

全球首款3D原子級(jí)硅量子芯片架構(gòu)正式問世,這一突破性進(jìn)展標(biāo)志著量子計(jì)算技術(shù)從實(shí)驗(yàn)室研究邁向了產(chǎn)業(yè)化應(yīng)用的關(guān)鍵一步。該架構(gòu)不僅展現(xiàn)了原子尺度上硅基量子比特的精確操控能力,更通過三維堆疊設(shè)計(jì)大幅提升了芯片的集成密度與運(yùn)算潛力,為量子計(jì)算服務(wù)的商業(yè)化落地奠定了堅(jiān)實(shí)基礎(chǔ)。

傳統(tǒng)硅基芯片技術(shù)已接近物理極限,而量子計(jì)算憑借其并行處理與指數(shù)級(jí)加速能力,被視為下一代信息技術(shù)的核心引擎。此次問世的3D原子級(jí)架構(gòu),在單原子級(jí)別上實(shí)現(xiàn)了量子比特的排列與控制,通過離子注入與原子級(jí)刻蝕技術(shù),將量子比特嵌入硅晶體晶格中,確保了極高的穩(wěn)定性和相干時(shí)間。三維垂直集成技術(shù)克服了平面布局的面積限制,使量子比特?cái)?shù)量得以規(guī)模化擴(kuò)展,為構(gòu)建大規(guī)模容錯(cuò)量子計(jì)算機(jī)提供了可行路徑。

這一突破對(duì)量子計(jì)算技術(shù)服務(wù)領(lǐng)域具有深遠(yuǎn)影響。硅基工藝與現(xiàn)有半導(dǎo)體產(chǎn)業(yè)高度兼容,有望大幅降低量子芯片的制造成本,加速其普及進(jìn)程。3D架構(gòu)提升了芯片的互聯(lián)效率與信號(hào)傳輸速度,為復(fù)雜量子算法的運(yùn)行提供了硬件支持。基于該架構(gòu)的量子計(jì)算云服務(wù)、加密通信、藥物研發(fā)模擬等應(yīng)用將逐步落地,賦能金融、醫(yī)療、材料科學(xué)等多個(gè)行業(yè)。

技術(shù)挑戰(zhàn)依然存在。原子級(jí)制造的良率控制、量子糾錯(cuò)的系統(tǒng)集成、以及低溫運(yùn)行環(huán)境的工程優(yōu)化等問題仍需持續(xù)攻關(guān)。業(yè)界需在硬件研發(fā)的加強(qiáng)軟件工具鏈與算法生態(tài)的建設(shè),推動(dòng)量子計(jì)算服務(wù)從“可用”向“好用”演進(jìn)。

首款3D原子級(jí)硅量子芯片架構(gòu)的誕生,是量子計(jì)算技術(shù)服務(wù)發(fā)展的重要里程碑。它不僅是科學(xué)前沿的突破,更為產(chǎn)業(yè)融合開辟了新賽道。隨著全球科研機(jī)構(gòu)與企業(yè)加速布局,量子計(jì)算有望在十年內(nèi)實(shí)現(xiàn)特定領(lǐng)域的應(yīng)用突破,重塑人類社會(huì)的計(jì)算范式。